続いてチュートリアルとして提供されているサンプルの実行をやってみる。

以下のページを元に実施した。

前準備

サンプルデザインをダウンロードして、適当なフォルダに解凍。

carry_lookahead_addr-mainとなっているのでサブフォルダをcarry_lookahead_adderにリネームしておく。

サンプル環境は、carry_lookahead_adderで以下のような構成になっている。

carry_lookahead_adder

| |

SystemVerilog VHDL_SystemVerilog

| | | | | |

design sim testbench design sim testbench

designとtestbenchのソースを引っ張ってきて、sim以下をworkとしてシミュレーションを実行する構成。

シミュレーションの実行

以下VSC上から作業する。

ファイル

→フォルダを開く

→carry_lookahead_adderの階層を指定

→VSCのエクスプローラーにフォルダが取り込まれる

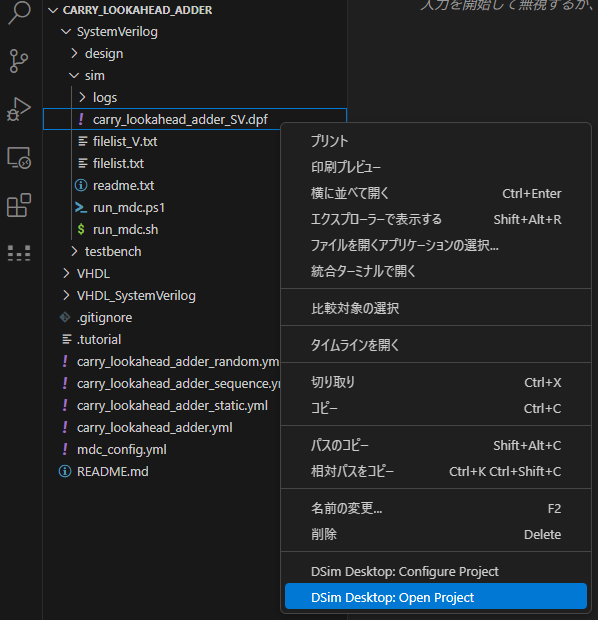

→SystemVerilog/sim/carry_lookahead_adderを右クリックし、Dsim Desktop:Open Projectを選択

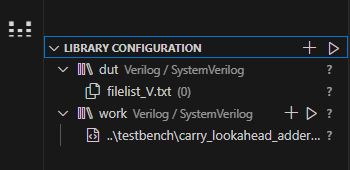

Dsimのextentionにファイル類が読み込まれる

→LIBRARY CONFIGURATIONの横にある三角のCompile Projectをクリック

→dutやworkの横にチェックマークがつけばOK

出力は以下のようになっていた。

$ dvlcom -lib 'dut' -F 'filelist_V.txt'

=N:[LibUpdate] Updated library dut.

$ dvlcom '..\testbench\carry_lookahead_adder_directed_tb.sv'

=N:[LibUpdate] Updated library work.

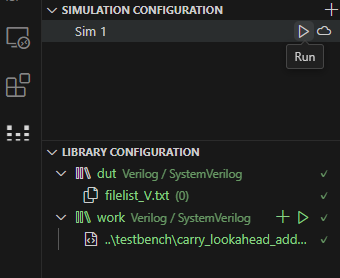

simの実行

SIMULATION CONFIGURATIONのSim 1の横にあるRunをクリック

以下のように出力されてsimが正常に実行された。

$ dsim -top work.carry_lookahead_adder_tb -L dut +acc+b -waves waves.mxd

=N:[UsageMeter XXX] usage server initial connection

=N:[License]

Licensed for Metrics Design Automation.

=N:[License] New lease granted.

Analyzing...

Elaborating...

Top-level modules:

$unit

carry_lookahead_adder_tb

Found 6 unique specialization(s) of 6 design element(s).

Optimizing...

Building models...

PLI/VPI access: +b

Simulation time precision is 1ns.

[1/5] module $root: 98 functions, 231 basic blocks

[2/5] module $pkgs: 1 functions, 2 basic blocks

[3/5] CU scope $unit: 1 functions, 2 basic blocks

[4/5] module carry_lookahead_adder_tb#(3): 9 functions, 51 basic blocks

[5/5] package std: 23 functions, 64 basic blocks

Linking image.so...

Using default typical min/typ/max.

=S:Begin run-time elaboration and static initialization...

=N:[dumpMXD] preparing MXD dump to 'waves.mxd'.

=N:[dump] Dump started at time 0

=N:Starting event scheduler...

[5 ns] [carry_lookahead_adder_tb/Checker] Info: Sum is correct: r_add1=0, r_add2=0, result=0

[10 ns] [carry_lookahead_adder_tb/Stimulus] New values r_add1=0, r_add2=0

[15 ns] [carry_lookahead_adder_tb/Checker] Info: Sum is correct: r_add1=0, r_add2=0, result=0

・・・・

6390 ns] [carry_lookahead_adder_tb/Stimulus] New values r_add1=7, r_add2=6

[6395 ns] [carry_lookahead_adder_tb/Checker] Info: Sum is correct: r_add1=7, r_add2=6, result=13

[6400 ns] [carry_lookahead_adder_tb/Stimulus] New values r_add1=7, r_add2=7

[6405 ns] [carry_lookahead_adder_tb/Checker] Info: Sum is correct: r_add1=7, r_add2=7, result=14

Test: PASSED (0 errors encountered)

=N:[dumpMXD] closing MXD dump

=T:Simulation terminated by $finish at time 6410 (..\testbench\carry_lookahead_adder_directed_tb.sv:80);

Run directory: XX:\carry_lookahead_adder\SystemVerilog\sim

System timescale is 1ns / 1ns

Metrics DSim version: 20240923.2.0

Random seed: (defaulted to 1)

dsim -top work.carry_lookahead_adder_tb -L dut +acc+b -waves waves.mxd というコマンドで実行しているようだ。

タイムスケールは1ns/1ns、波形はmxd形式でダンプ、他にも実行Dirやツールバージョンなども出力されていて、思ったよりしっかりしている。

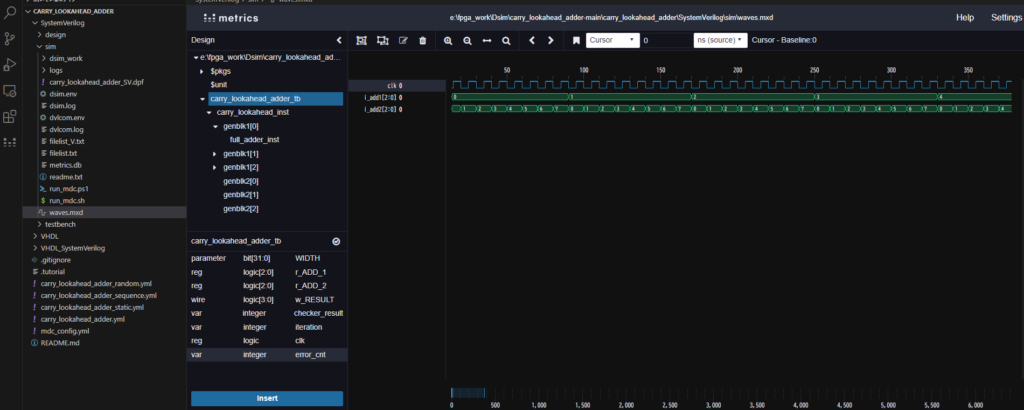

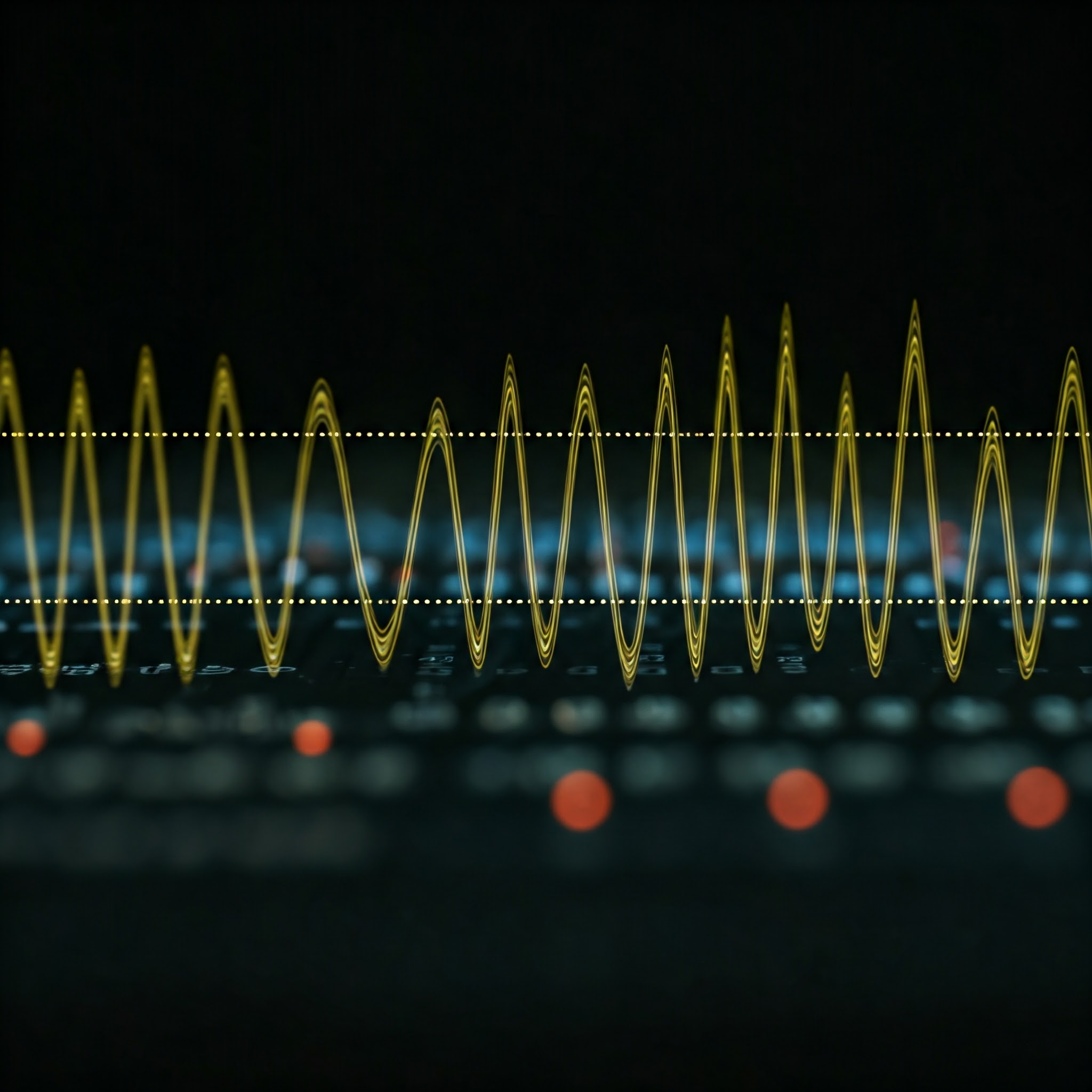

波形の確認

VSCのエクスプローラーに戻って、System verilog/sim以下にwave.mxdというファイルが生成されているのでクリック

→波形viewerが立ち上がって、ポチポチ選択して、Insertとかやると波形が見れるようになる

これはかなりすごい!

操作も直観的でわかりやすいし、動作的にもそんなに重い感じもない。

ちょっと触った感じやりたいことは大体できそうだった。

あまり期待してなかっただけに良い意味で驚いた。

実行時のオプション変えればvcdも生成できるらしい。

今回はVSCからポチポチして、コンパイルやシミュレーションを実行したが、コマンドを使いこなせばターミナルからも使えそうなので、今度試してみたい。

vivadoとかに依存せず、RTLコーディングして、デバッグして、合成手前まで持っていける環境は作れそうだ。

Dsimのサービスが続いてくれるといいな。

コメント